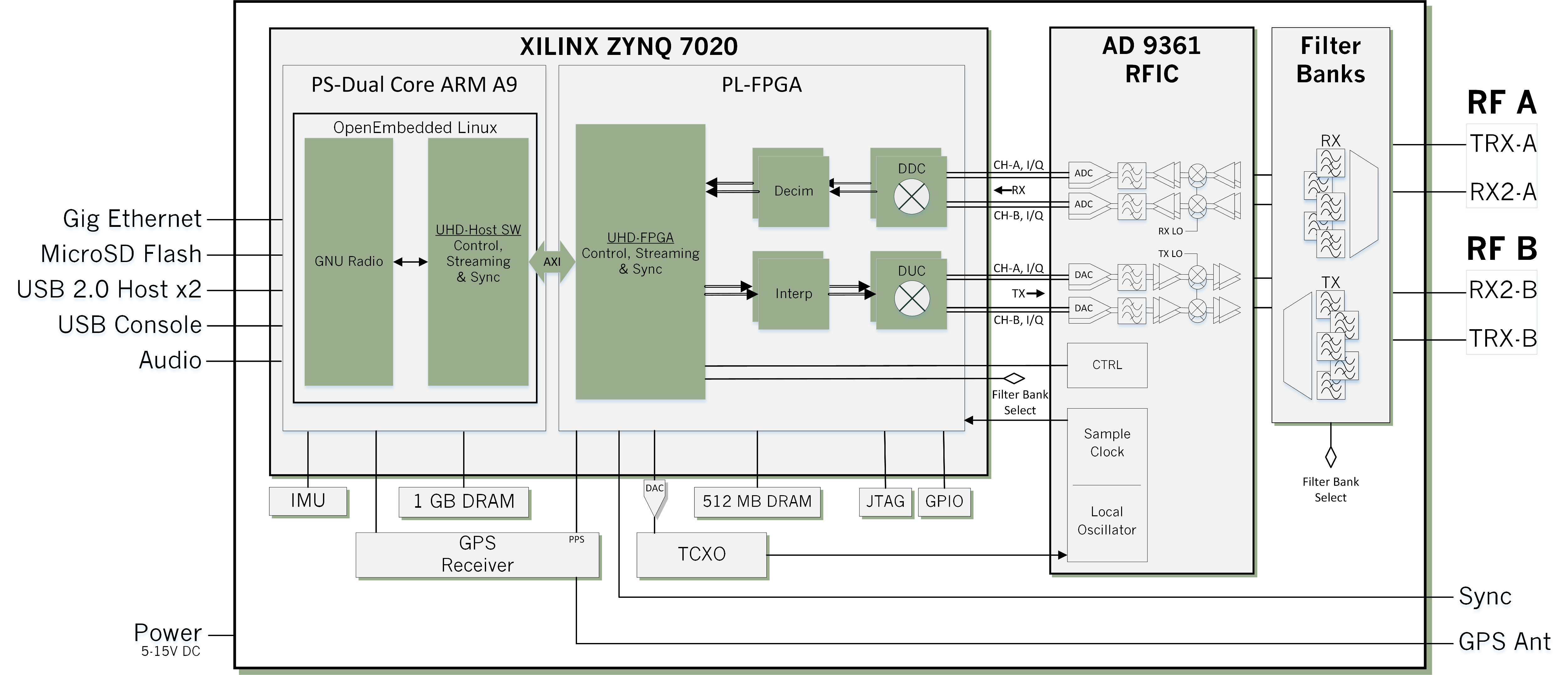

andre19 Posted June 20, 2019 Share Posted June 20, 2019 Hi! In previous topic i have asked about first start with Zynq core (i have Ettus E310 board) Now it is time for connecting ADC that is on board AD9361 . I want to get some signal and receive it via ADC - i do not understand how to connect ADC (how to edit Zynq for getting data via RF board connector (via LVDS??) https://files.ettus.com/schematics/e310/e310.pdf) I have read manual (p.34) about that ADC https://www.analog.com/media/en/technical-documentation/data-sheets/AD9361.pdf I hope, somebody help me to edit blocks or code in Vivado and get digitalized data from ADC. Best regards. Link to comment Share on other sites More sharing options...

jpeyron Posted June 21, 2019 Share Posted June 21, 2019 Hi @andre19, We have not worked with the ETTUS 310. We would suggest reaching out to ettus's support since they would have more experience with this board. best regards, Jon Link to comment Share on other sites More sharing options...

andre19 Posted June 21, 2019 Author Share Posted June 21, 2019 Hi @jpeyron I have written for Ettus - them work with GNU Radio and don't work vith Vivado. They doesn't gave me any normal consultation about work Zynq with Vivado I started to program Zynq chip via Vivado - ( i have digilent Arty A7 board and now start to work with more power core) - there are different topics about programing Zynq via Vivado in your forum. I hope, somebody from forum explain for me how to corect edit blocks in Vivado for getting data from ADC I have find schematic of conection ADC to Zynq https://www.analog.com/media/en/technical-documentation/data-sheets/AD9361.pdf (http://files.ettus.com/schematics/e310/e310_db.pdf - i need SPI and P0 for receive data manual p.1) But i don't understand how true configure Zynq pins in VIVADO for receivered data (I don't worked with analogy types of getting data. I have experiment with STM32 - i writed adrres and read data from ADC - simple) I do not understand what to configure inside the kernel to receive information from the ADC - my problem it is low knowledge in configuration Zynq for receive data(( So far I can not understand in what sequence and what levels to put on the pins to start receiving data from the ADC. Best regards Link to comment Share on other sites More sharing options...

jpeyron Posted June 25, 2019 Share Posted June 25, 2019 Hi @andre19, This is beyond the scope of the Digilent forums. We do not have the bandwidth to configure the ZYNQ processor, generate a working XDC and facilitate a XADC project for a non-Digilent FPGA. We do have the bandwidth to help with more specific questions. I would suggest reading at the ZYNQ Book and the Zynq-7000 SoC Design Hub - Boot and Configuration for configuring the ZYNQ processor. You can look at our ZYNQ processors board files, XDC's as good references for your ZYNQ Dev board. Here are our XADC projects. The Cora Z7-10 XADC demo should be a good example to look at for using the XADC IP with the ZYNQ processor. best regards, Jon Link to comment Share on other sites More sharing options...

andre19 Posted June 25, 2019 Author Share Posted June 25, 2019 Hi @jpeyron I will work with your information. Thanks! Link to comment Share on other sites More sharing options...

Question

andre19

Hi!

In previous topic i have asked about first start with Zynq core (i have Ettus E310 board)

Now it is time for connecting ADC that is on board AD9361 . I want to get some signal and receive it via ADC - i do not understand how to connect ADC (how

to edit Zynq for getting data via RF board connector (via LVDS??) https://files.ettus.com/schematics/e310/e310.pdf)

I have read manual (p.34) about that ADC https://www.analog.com/media/en/technical-documentation/data-sheets/AD9361.pdf

I hope, somebody help me to edit blocks or code in Vivado and get digitalized data from ADC.

Best regards.

Link to comment

Share on other sites

4 answers to this question

Recommended Posts

Archived

This topic is now archived and is closed to further replies.